(19) **日本国特許庁(JP)**

(51) Int. CL.

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4411436号 (P4411436)

(45) 発行日 平成22年2月10日(2010.2.10)

(24) 登録日 平成21年11月27日(2009.11.27)

\_\_\_\_\_

HO2M 3/135 (2006.01)

HO2M 3/135

FL

U

請求項の数 5 (全 13 頁)

(21) 出願番号 特願2004-268376 (P2004-268376)

(22) 出願日 平成16年9月15日 (2004.9.15) (65) 公開番号 特開2006-87197 (P2006-87197A)

(43) 公開日 平成18年3月30日 (2006. 3. 30) 審査請求日 平成19年2月22日 (2007. 2. 22) ||(73)特許権者 504145308

国立大学法人 琉球大学 沖縄県中頭郡西原町字千原1番地

||(74)代理人 100104341

弁理士 関 正治

(72) 発明者 千住 智信

沖縄県宜野湾市志真志1-10-4-40

1 志真志住宅

∥(72)発明者 金城 達人

沖縄県豊見城市字我那覇528-2 2 F

審査官 槻木澤 昌司

最終頁に続く

(54) 【発明の名称】双方向DC-DCコンバータのソフトスイッチング回路

## (57)【特許請求の範囲】

## 【請求項1】

入力側正極端子と負極端子および出力側正極端子と負極端子を有し、前記入力側負極端子にアノードを接続し前記出力側正極端子にカソードを接続した第1ダイオード、前記出力側負極端子にアノードを接続し前記入力側正極端子にカソードを接続した第2ダイオード、前記入力側正極端子と前記出力側正極端子の間に設けられた第1半導体スイッチ、および前記出力側負極端子と前記入力側負極端子の間に設けられた第2半導体スイッチにより構成される双方向DC-DCコンバータにおいて、

前記第1半導体スイッチに直列に第1共振用インダクタを設け、前記第2半導体スイッチに直列に第2共振用インダクタを設け、出力側正極端子と出力側負極端子の間に共振用キャパシタを設け、前記第1半導体スイッチと第2半導体スイッチを共振電流がゼロのときに作動させる制御器を備えたことを特徴とする電流共振形の双方向DC-DCコンバータのソフトスイッチング回路。

# 【請求項2】

前記第1半導体スイッチはアノードを前記入力側正極端子の方に向けカソードを前記出力側正極端子の方に向けたGTOサイリスタ、前記第2半導体スイッチはアノードを前記出力側負極端子の方に向けカソードを前記入力側負極端子の方に向けたGTOサイリスタであることを特徴とする請求項1記載の双方向DC-DCコンバータのソフトスイッチング回路。

【請求項3】

前記共振用キャパシタの容量をCrとしたとき、Crは、入力電圧をVin、出力端子に接続した直流出力電流をIdc、第1,第2の共振用インダクタのインダクタンスをそれぞれLr1, Lr2とするときに、不等式

Cr  $(Idc/Vin)^2 (Lr1+Lr2)$

で表される関係を有するようにすることを特徴とする請求項1または2記載の双方向DC-DCコンバータのソフトスイッチング回路。

#### 【請求項4】

電力貯蔵要素を前記入力側正極および負極端子に接続し、前記出力陽極端子は出力インダクタを介しまた前記出力負極端子は直接に電流形インバータに接続することにより、電力貯蔵装置を形成したことを特徴とする請求項1から3のいずれかに記載の双方向DC-DCコンバータのソフトスイッチング回路。

【請求項5】

前記電力貯蔵要素は、電気二重層キャパシタを複数用いて形成されるキャパシタバンクで構成されることを特徴とする請求項4記載の双方向DC-DCコンバータのソフトスイッチング回路。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、電流形インバータに接続する双方向DC - DCコンバータのソフトスイッチング回路に関し、特に充電可能な電力貯蔵装置に最適に用いることができる双方向DC - DCコンバータのソフトスイッチング回路に関する。

【背景技術】

[0002]

近年、パワーエレクトロニクス技術の進歩を背景に、種々の大容量電力貯蔵装置が開発されている。現状で実用化されている大容量電力貯蔵装置に揚水発電所があるが、今後の建設は難しく発展性がない。また二次電池は環境への影響などが心配される。

近年、数 1 0 0 0 μ F オーダー以上という驚異的な静電容量を持つ電気二重層キャパシタ(EDLC)素子が出現し、これにパワーエレクトロニクス技術を利用することにより、二次電池に匹敵するエネルギ密度や出力密度を有する大容量電力貯蔵装置が開発されている。

[0003]

一般に、電気二重層キャパシタバンクを利用した電力貯蔵装置(ECaSS)には電圧形インバータが用いられるが、単セルの耐電圧が3V以下でエネルギ放電に伴う端子電圧の低下が無視できないEDLC固有の特性に伴う直流リンク電圧の低下、出力低下、出力制御の困難性などの欠点が存在する。

発明者らは、ECaSSに電流形インバータを適用することによりこれらの欠点を解消する研究を行ってきた。電流形インバータは、過電流保護が容易、分散型電源に使用するときに単独運転の危険性が無いなど、電圧形インバータにない利点を有する。電流形インバータでは、直流電流の方向が変化せず、直流リンク電圧の極性を変化させることで電力の授受を行うため、充放電を行うには直流部に双方向DC-DCコンバータを設ける。

[0004]

電流形インバータを用いる利点として、(1)比較的小さい直流入力電圧で大容量の電力を出力できる、(2)エネルギ放電に伴うEDLCの端子電圧が低下して直流リンク電圧が変動した場合でも低出力を維持できる、(3)直流部に接続する双方向DC-DCコンバータを用いて直流電流制御を行うことによってEDLCの内部抵抗損失を低減することができる、などを挙げることができる。

このように、電力貯蔵装置には電流形インバータの使用が好ましく、電流形インバータの汎用性の向上と変換効率の向上が求められている。特に、分散型電源には電流形インバータをパワーコンデショナーとして利用することが有利で、電力業界でも電流形インバータの需要がますます増大すると予測される。

10

20

30

40

#### [0005]

しかし、自励式半導体素子を用いてハードスイッチングする電流形インバータでは、スイッチングによる電力損失が大きいためエネルギ変換効率が低く、また急峻な電圧・電流波形を生じるため装置ストレスが大きく製造コストが高くついた。さらに、電磁妨害(EMI)を発生するため、環境性にも問題があった。

スイッチング損失を低減し電磁妨害を抑制するため、共振を用いて、電流あるいは電圧がゼロのときにスイッチング素子をオン・オフするソフトスイッチング手法が用いられる。しかし、半導体素子および共振素子からなる回路構成が複雑となる。また、簡単な回路としては、双方向性を持たない無効電力制御に限定するものしかなかった。さらに、電力貯蔵装置に適用するには、電力の充放電を可能とする双方向性の共振回路構成が難しいため、大電力を扱う分野において、このような共振回路が実用化された例はなかった。

10

#### [0006]

特許文献1には、電流形インバータに相当するDCリンク・LC直列共振形の高周波共振リンクを持つ電力変換装置において、ソフトスイッチングを利用し直流電源への電力回生が可能な回路が開示されている。

開示された回路は、LC直列共振回路中に共振コンデンサの充放電を制御するスイッチ素子を備えると共に、直流電流供給用インダクタと磁気的に密結合したフィードバック用インダクタとダイオードの直列回路を直流電源に並列接続したもので、電源装置から供給される直流電流がゼロになるとレンツの法則に従ってフィードバック用インダクタに大きなフィードバック電流が流れてバッテリに余剰電力が回生される。

20

## [0007]

開示された電流形インバータは、インバータのサイリスタがソフトスイッチングを行うためスイッチング損失が小さくなりインバータ効率が向上し、またスイッチングによるEMIが発生しない。

しかし、開示回路では共振回路部に双方向性を与えることができないため、バッテリから供給される電流によってフィードバック用インダクタに発生する起電力による電流を電力回生するだけで、系統側で発生する余剰電力を吸収する機構になっていない。

[00008]

特許文献 2 には、商用電源の配電網から離れた離島などで利用できる発電設備が開示されている。この開示装置は、太陽光や風力など自然エネルギを利用する主発電装置の出力が不足する毎に起動されて主発電装置の出力が回復するまで運転する化石燃料で運転される補助発電装置を組み合わせたもので、補助発電装置の起動過渡期間の電力補償エネルギを保持するキャパシタバンクと双方向コンバータを備える。

30

# [0009]

自然エネルギを利用する主発電装置の出力不足を検知すると、双方向コンバータのインバータ運転によりキャパシタバンクの直流出力を定電圧制御して交流化し、配電線に供給して出力を補うことができる。また、主発電装置の出力に余剰があるときは、コンバータ運転して配電線の交流電力の一部を充電用の直流電力に変換してキャパシタバンクを充電する。双方向コンバータ内部の回路は開示されていないが、放電と充電を切り換えるために、充電路ダイオードと放電路スイッチを並列に組んだ回路が用いられる。この切り換え回路は電流共振形でなく、放電路スイッチは放電期間中は常時オンにすればよいので、ソフトスイッチングする要請は少ない。

40

なお、補助発電装置の起動過渡期間は数秒であるので、キャパシタバンクは大きな電力 貯蔵を必要としない。

【特許文献1】特開平8-51781号公報

【特許文献2】特開2001-136681号公報

【発明の開示】

【発明が解決しようとする課題】

#### [0010]

本発明が解決しようとする課題は、電力貯蔵装置に適用する電流形インバータにおいて

、ソフトスイッチングを可能とする簡素な共振回路を提供することであり、特に直流リンク部に使用する双方向 D C - D C コンバータについて共振を用いたソフトスイッチングが可能な共振回路を提供することである。

# 【課題を解決するための手段】

# [0011]

上記課題を解決するため、本発明の双方向DC-DCコンバータのソフトスイッチング回路は、入力側負極端子にアノードを接続し出力側正極端子にカソードを接続した第1ダイオード、出力側負極端子にアノードを接続し入力側正極端子にカソードを接続した第2ダイオード、入力側正極端子と出力側正極端子の間に設けられた第1半導体スイッチ、および出力側負極端子と入力側負極端子の間に設けられた第2半導体スイッチにより構成された双方向DC-DCコンバータにおいて、第1半導体スイッチに直列に第1共振用インダクタを設け、第2半導体スイッチに直列に第2共振用インダクタを設け、出力側正極端子と出力側負極端子の間に共振用キャパシタを設けて、充放電中に発生させた共振電流がゼロのときに第1半導体スイッチと第2半導体スイッチを作動させるようにしたことを特徴とする。

#### [0012]

放電期間には、第2半導体スイッチをオン状態に維持して、予め決められたタイムスケジュールにしたがって共振電流がゼロのときに第1半導体スイッチを開閉し、電流共振形降圧コンバータとして動作させる。また、充電期間には、第1半導体スイッチをオフ状態にして、予め決められたタイムスケジュールにしたがって共振電流がゼロのときに第2半導体スイッチを作動させ、電流共振形昇圧コンバータとして動作させる。

本発明の回路を有する双方向 D C - D C コンバータは、充電方向と放電方向で同一の共振素子を用いた簡素な双方向性の共振回路を構成し、共振電流がゼロになるタイミングで 半導体スイッチを動作させてソフトスイッチングを可能とすることができる。

#### [0013]

したがって、スイッチングによる電力損失を抑制してエネルギ変換効率を向上させ、電磁妨害も十分抑制することができる。

本発明に係る双方向 D C - D C コンバータを、電力貯蔵要素と電流形インバータの間に配置する直流リンクとして使用すると、電力貯蔵要素から電流形インバータに直流電力を供給する放電工程と、系統からインバータを介して余剰電力を電力貯蔵要素に電力回生する充電工程の双方向に流通させることができる。

また、急峻な電圧・電流波形が生じないので、回路素子は高度な耐性を要求されず、簡素な回路構成と相俟って製造コストも低下する。

### [0014]

本発明の双方向DC - DCコンバータのソフトスイッチング回路では、半導体スイッチがGTOサイリスタであって、第1半導体スイッチはアノードを入力側正極端子の方に向けカソードを出力側正極端子の方に向け、第2半導体スイッチはアノードを出力側負極端子の方に向けカソードを入力側負極端子の方に向けて接続されるようにしてもよい。

本発明の回路では、充電放電のいずれにおいても半導体スイッチを通る直流電流の向きが変わらないので、半導体スイッチとして双方向性を持つものに限らず 1 方向にしか電流を流さないものであってもよい。半導体スイッチとして、サイリスタ、パワートランジスタ、IGBTなどを使用できるが、特に大容量の電流を制御できるGTOサイリスタを使用して大容量電力貯蔵装置に適用することができる。

# [0015]

共振用キャパシタの容量Crは、入力電圧をVin、出力端子に接続した直流出力電流をIdc、第1,第2の共振用インダクタのインダクタンスをそれぞれLr1,Lr2とすると、不等式 Cr (Idc/Vin)<sup>2</sup> (Lr1+Lr2)

で表される関係を有するようにすることが好ましい。

この関係が成立すれば、共振電流を得て、共振周波数より小さいスイッチング周波数を 設定することができる。 10

20

30

40

なお、第1共振用インダクタのインダクタンスLr1は、第2共振用インダクタのインダクタンスLr2より小さく選択することが好ましい。放電時の共振電流の振幅は(Cr / (Lr1+Lr2))  $^2$  Vinに比例し、充電時は(Cr / Lr2)  $^2$  Vinに比例するので、Lr1を小さくして充電時と放電時の共振電流の振幅を抑制できれば、スイッチの電流ストレスが低減するからである。

#### [0016]

本発明の双方向DC-DCコンバータのソフトスイッチング回路を電力貯蔵要素と電流 形インバータの間に配置して、電力貯蔵装置用電流形インバータを構成することができる

なお、電力貯蔵要素として、電気二重層キャパシタを複数用いて形成されるキャパシタ バンクを用いると、小型で大容量の電力貯蔵が可能となり、様々な分野で有効に利用でき る。

#### 【発明の効果】

# [0017]

本発明の電流共振形を用いれば、回路構成が簡単で、半導体スイッチのソフトスイッチングを行うことでスイッチング損失を低減してエネルギ変換効率を向上させ、電磁妨害も 殆ど生じないような電力貯蔵装置を提供することができる。

なお、本発明の双方向 D C - D C コンバータは、分散型電源のパワーコンデショナとして利用することも可能で、また、直流機器用の変換器として利用することもできる。

# 【発明を実施するための最良の形態】

### [0018]

以下、実施例を用いて本発明を詳細に説明する。

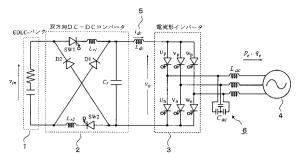

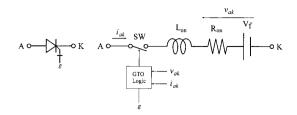

図1は、本実施例に係る双方向DC-DCコンバータのソフトスイッチング回路を組み 込んでなる電流形電力貯蔵装置の主回路構成図である。

本実施例に係るソフトスイッチング回路を備えた双方向DC-DCコンバータ2は、直流電源部1とインバータ部3の間の直流リンク部に配置され、全体で電力貯蔵装置を構成して、三相誘導電動機4などの負荷に交流電力を供給する。

直流電源部1は、電気二重層キャパシタ(EDLC)を用いたキャパシタバンクで構成され、直流端子電圧Vinを発生する。なお、キャパシタバンクは内部抵抗を有するので、回路図には等価的な抵抗を表示してある。

直流電源部1の正負の出力端子は、それぞれ直流リンク部2の正負の入力端子に接続される。

#### [0019]

直流リンク部に設けた双方向 D C - D C コンバータ 2 は、第 1 整流ダイオードD1、第 2 整流ダイオードD2、 G T O サイリスタで構成された第 1 半導体スイッチSW1、および G T O サイリスタで構成された第 2 半導体スイッチSW2を備える。本実施例の双方向 D C - D C コンバータ 2 は、さらに第 1 共振用インダクタLr1、第 2 共振用インダクタLr2、および共振用キャパシタCrを新たに備えたことを特徴とする電流共振形第 1 - 4 象限 D C - D C コンバータである。

## [0020]

第1整流ダイオードD1は、双方向 D C - D C コンバータ 2 の入力側負極端子にアノードを接続し出力側正極端子にカソードを接続し、第2整流ダイオードD2は、出力側負極端子にアノードを接続し入力側正極端子にカソードを接続する。第1半導体スイッチSW1の G T O サイリスタは、入力側正極端子にアノードを接続し出力側正極端子にカソードを接続する。また、第2半導体スイッチSW2は出力側負極端子にアノードを接続し入力側負極端子にカソードを接続する。

## [0021]

さらに、第1共振用インダクタLr1を第1半導体スイッチSW1と直列に接続し、第2共振用インダクタLr2を第2半導体スイッチSW2と直列に接続し、共振用キャパシタCrを出力側正極端子と出力側負極端子の間に設けている。

10

20

30

40

第1半導体スイッチSW1と第2半導体スイッチSW2を操作することにより充電と放電を選択すると共に、充電・放電の工程中ではソフトスイッチングによりオンオフ操作することによりスイッチング損失を抑制して、変換効率を向上させす。

充電時と放電時で同じ共振素子(Lr1, Lr2, Cr)を用いて回路構成を単純化している。

# [0022]

直流リンク部2の出力側正極端子は直流インダクタLdc5を介して電流形インバータ3の正極入力端子に接続し、直流リンク部2の出力側負極端子は直接に電流形インバータ3の負極入力端子に接続する。電流形インバータ3、半導体スイッチを駆動して直流交流変換して出力し、インダクタLacとキャパシタCacで構成される交流フィルタ6を介して3相交流電力を電動機などの負荷4に供給する。

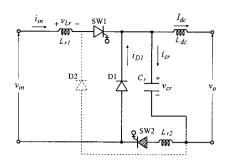

[0023]

図 2 は、双方向 D C - D C コンバータ 2 の第 4 象限動作時であって充電時の等価回路を表す。

充電時には、第1半導体スイッチSW1をオフ状態にし(図中点線で表示した)、第2半導体スイッチSW2をプログラムにしたがってオンオフ操作することによって(図中斜線ハッチングを入れて表示した)、第2整流ダイオードD2の働きと相俟って、電流共振形昇圧コンバータとして動作させる。図中矢印の左側の回路は、右側の回路に等価変換される。直流インダクタLdcを通る直流電流Idcは、放電時と同じように図の右方向に流れるが、系統側からの余剰電流は共振キャパシタCrに充電されキャパシタ電圧Vcrが増加して入力電圧Vinを越えると第2整流ダイオードD2が順バイアスされて直流電源部1のキャパシタバンクに回生電力として充電される。

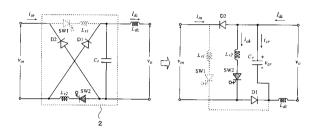

[0024]

一方、図3は、双方向DC-DCコンバータ2の第1象限動作時であって放電時の等価回路を表す。

放電時には、第2半導体スイッチSW2を期間中オン状態にし(図中斜線ハッチングを入れて表示した)、第1半導体スイッチSW1をプログラムにしたがって駆動することによって、第1整流ダイオードD1の働きと相俟って、電流共振形降圧コンバータとして動作させる。

また、充電時と放電時で直流インダクタLdcを通る電流の向きは変わらない。

[0025]

双方向 D C - D C コンバータ 2 は電流共振形になるため、充電時と放電時のソフトスイッチング手法は動作波形が類似しているので、充電時における動作解析結果について説明する。

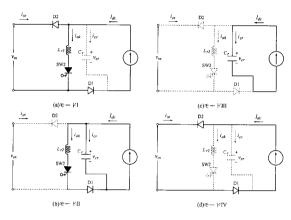

充電時は、各スイッチング周期毎に、インダクタ励磁期間のモードI、共振期間のモードII、キャパシタ放電期間のモードIII、整流ダイオードオン期間のモードIVの4つのモードに分けられる。

[0026]

図4は、充電時におけるモード別の等価回路を表す。(a)図はモードI、(b)図はモードII、(c)図はモードIII、(d)図はモードIVの等価回路である。充電時には、第1半導体スイッチSW1はオフ状態になっている。

ここでは、各モードにおける第 2 半導体スイッチSW2に使われるGTOサイリスタにおける瞬時電圧 akと瞬時電流 i ak、およびスイッチング損失(電力損失) boを導出する

[0027]

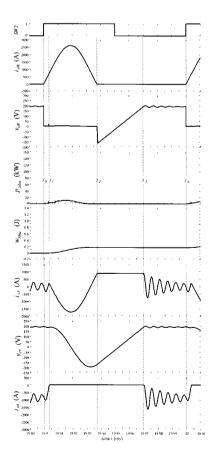

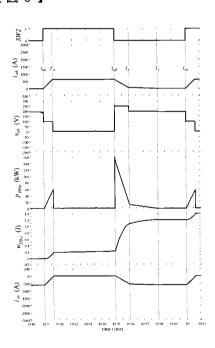

図5は、シミュレーションにより得られた、充電時の1スイッチング期間における各部の瞬時電圧・電流の波形図である。図は、横軸に時間 t をとり、第2半導体スイッチ(G T O サイリスタ)SW2のオンオフ指令信号の状態、第2半導体スイッチSW2を通る共振電流の瞬時値 i ak、第2半導体スイッチSW2に掛かる電圧の瞬時値 ak、第2半導体スイッチSW2における瞬時電流iakと瞬時電圧 akを掛けて得られるソフトスイッチングを用いたときの消費電力PSbo、消費電力PSboを時間積分して得られるエネルギ損失量WSbo、共振用キ

10

20

30

40

10

20

30

40

50

ャパシタCrへの充電電流icr、共振用キャパシタCrの端子間電圧 cr、および電力貯蔵要素からの入力電流iinの時間変化を表示している。なお、時間軸方向には、縦の点線でモードを区切る時刻T0,T1,T2,T3,T4の位置を示している。

#### [0028]

シミュレーションは、直流電流Idcが変化しないと仮定し、GTOサイリスタが図7の 等価回路図に表したようにスイッチに対して直列に内部インダクタンスLonと内部抵抗Ron と順方向電圧Vfを有するとし、図8のパラメータ表の値を用いて、瞬時シミュレーション ソフトウェアMATLAB/SIMULINKおよびSimPowerSystemsにより行った。

#### [0029]

なお、比較のため、図6にハードスイッチング手法による充電時の瞬時電圧・電流等を示した。図は横軸に時間tを取って、第2半導体スイッチSW2のオンオフ状態、第2半導体スイッチSW2の瞬時電流iak、瞬時電圧 ak、第2半導体スイッチSW2におけるハードスイッチング時の消費電力PHbo、ハードスイッチング時のエネルギ損失量WHbo、および電力貯蔵要素からの入力電流iinの時間変化を表示している。モードの区切り時刻を縦の点線で示してある。

#### [0030]

(1)モードI:インダクタ励磁期間(T0<t<T1)</li>

図5における時刻T0から時刻T1の期間であって、第2半導体スイッチSW2を通る瞬時電流iakがゼロである時刻T0において第2半導体スイッチSW2がターンオンされて、図4(a)に示す等価回路状態になり、直流電流Idcが第2半導体スイッチSW2に転流されて第2整流ダイオードD2のアノード電圧が電力貯蔵要素の端子電圧 inに達して、第2整流ダイオードD2がオフとなってモードIIに切り替わるまでの期間である。

## [0031]

モードIでは、瞬時電流iakと瞬時電圧 akは、(1)式で表されるものとなる。

iak = in/Lr2\*(t-T0)

ak = Ron \* iak + Vf

(1)

また、(1)式より、モード」におけるエネルギ損失は、

Wbo1 = Pbo1(t) dt = iak(t) ak(t) dt

$= Ron / 3( in / Lr2)^{2} (T1 - T0)^{3} + inVf / 2Lr2(T1 - T0)^{2} (2)$

# で表される。

これらの変化は、図5に表されている。

# [0032]

(2)モードII:共振期間(T1<t<T2)

図 5 における時刻 T 1から時刻 T 2の期間であって、第 2 整流ダイオードD2がオフとなって図 4 ( b )に示す等価回路状態になり、 C r と L r 2により C L 共振する期間である。共振電流がゼロになったときに次のモードIIIに切り替わる。

モードIIでは、瞬時電流iakと瞬時電圧 akは、(3)式で表されるものとなる。

$iak = Idc + (Cr/Lr2)^{1/2}$  insin rbo(t - T1)

ak = Ron \* i ak + Vf (3)

ここで、 rboは共振角周波数で、1 / (Lr2 Cr) <sup>1 / 2</sup> により表される。

## [0033]

(3)式より、モードIIにおけるエネルギ損失Wbo2は、

Wbo2 = Pbo2(t) dt = iak(t) ak(t) dt

=  $Ron[Idc^{2}(T2 - T1) + 2 inIdc C r{1 - cos rbo(T2 - T1)}$

+  $in^2 C r / Lr2\{(T2 - T1) / 2 - sin2 r (T2 - T1) / 4 rbo2\}$

$+Vf[Idc(T2 - T1) + inCr{1 - cos rbo(T2 - T1)}]$  (4)

で表される。これらの変化は、図5に表されている。

## [0034]

(3)モードIII:キャパシタ放電期間(T2<t<T3)</li>

図 5 における時刻 T 2から時刻 T 3の期間であって、共振電流 i akがゼロとなった時刻 T

2に第2半導体スイッチSW2がゼロ電流スイッチング(ZCS)でターンオフされ図4(c)に示す等価回路状態になる。

モードIIIでは、瞬時電流iakと瞬時電圧 akは、(5)式で表されるものとなる。

iak = 0

ak = Ron \* i ak + Vf (5)

### [0035]

(5)式より、電流がゼロであるので、モードIIIにおけるエネルギ損失Wbo3はゼロである。

$$Wbo3 = Pbo2(t) dt = iak(t) ak(t) dt$$

$$= 0$$

(6)

モードIIIの期間で、共振キャパシタに電気エネルギが充電されて共振キャパシタCrの端子電圧 crが増加し始める。端子電圧 crが入力電圧 inに達するとモードIVに移行する。

# [0036]

(4) モードIV:整流ダイオードオン期間(T3<t<T4)

図5における時刻T3から時刻T4の期間であって、共振キャパシタCrの端子電圧 crが入力電圧 inに達して第2整流ダイオードD2が順バイアスされ導通すると、図4(d)に示す等価回路状態になる。モードIVでは、第2整流ダイオードD2が導通し直流電流Idcが転流して電気エネルギがキャパシタバンクに充電される。図4(d)と図5における電流の向きに注意すること。モードIVの期間中は瞬時電流iakがゼロなので、モードIIIのときと同様にエネルギ損失は発生しない。任意の時刻に第2半導体スイッチSW2をオンすることによりモードIに切り替わる。

## [0037]

スイッチング周波数 f sboは共振周波数 f rboより小さいことが好ましいので、充電時における共振電流式(3)より、

frbo =  $rbo/2 = 1/2 (Lr2Cr)^{1/2} > fsbo (7)$ となる。

また、放電時における共振電流iakは(8)式で表される。

$iak = Idc + (Cr/(Lr1 + Lr2))^{1/2}$  insin rbu(t - T1) (8)

したがって、放電時におけるスイッチング周波数 f sbuは、

f rbu = rbu / 2 = 1 / 2  $((Lr1 + Lr2) Cr)^{1/2} > f sbu (9)$

となる。ここで、 rb u は、1 / ((Lr1 + Lr2) C r) <sup>1 / 2</sup> により表される。

(7)式と(9)式から分かるように、スイッチング周波数は放電時と充電時では異なる値に設定しなければならない。この差は共振用インダクタンスLr1, Lr2に基づいて決まる。

## [0038]

次に、(3)式と(8)式の共振電流式から、ゼロ電流スイッチング(ZCS)を達成するためには、

$$Cr (Idc/in)^{2} (Lr1 + Lr2)$$

(10)

なる条件が満たされる必要がある。

(10)式における入力電圧 inは、電気二重層キャパシタバンクの端子電圧に相当する。バンク電圧はエネルギの放電に伴い減少するため、エネルギの充放電に伴い共振状態が変化する。

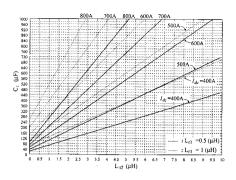

# [0039]

そこで、満充電時におけるバンク電圧を約200Vとして、電気エネルギを約95%放電した場合のバンク電圧60VについてZCS条件を考える。

(10)式で入力電圧 inを60 V とした場合の共振キャパシタ C r の値は図9に示すようになる。図9は、第1共振用インダクタLr1を1μH(図中実線で表示)あるいは0.5μH(図中点線で表示)に固定して、第2共振用インダクタLr2の値(横軸)を変化させたときに、ZCSを達成するために設定すべき共振用キャパシタCrの値を縦軸にプロ

20

30

40

ットしたものである。

第1共振用インダクタLr1と第2共振用インダクタLr2の組に対して共振用キャパシタCrの適切な設定値が直ぐに分かる。共振用キャパシタCrは、図中の線より大きい値に設定するとよい。

# [0040]

なお、放電時と充電時で共振電流の振幅差を小さくすることにより、スイッチの電流ストレスを軽減することができる。このため、第1共振用インダクタLr1と第2共振用インダクタLr2の関係を、

Lr2 > Lr1

(11)

となるように規制することが好ましい。

[0041]

双方向DC-DCコンバータにおけるエネルギ損失について検討する。

図8のパラメータ表の値を用いて先の演算式により算出した損失エネルギの理論値とシミュレーションにより得られた損失エネルギを比較すると、理論値とシミュレーション結果は放電時には、ソフトスイッチングを使ったときの理論値で0.0357Wに対してシミュレーションでは0.0430W、ハードスイッチングでは理論値で0.1755Wに対してシミュレーションで0.208Wと若干の差異が見られるが、充電時の値は、ソフトスイッチングで理論値が0174Wに対してシミュレーションでは0.181W、ハードスイッチングでは理論値で1.1019Wに対してシミュレーションで1.210Wと比較的よく一致している。

いずれのケースにおいても、ハードスイッチングよりソフトスイッチングの方がエネル ギ損失が格段に小さいことが分かる。

[0042]

なお、シミュレーションにより求めた充電時におけるハードスイッチングの効率が84.51%であるのに対してソフトスイッチングの効率が96.95%、放電時においてはハードスイッチングで84.48%に対してソフトスイッチングでは99.28%であることから、ソフトスイッチング化することにより効率改善が著しいことが分かる。

[0043]

電気二重層キャパシタバンク(EDLC)1はエネルギの充放電に伴い端子電圧が変化する。また、電流形インバータ3の直流電流Idcも充放電に伴い、あるいは有効・無効電力量に依存して変化する。

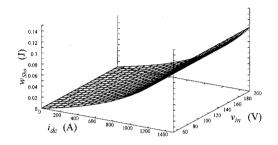

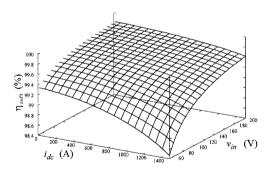

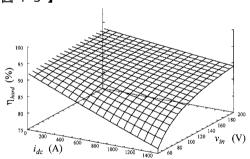

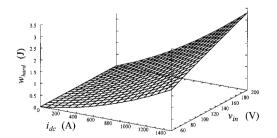

そこで、これらの要因に起因して変化するエネルギ損失値と変換効率について、図10から図13に示す。図10と図11はそれぞれ双方向DC-DCコンバータのソフトスイッチングにおけるエネルギ損失Wsboと変換効率 soft、図12と図13はハードスイッチングにおけるエネルギ損失Whardと変換効率 hardを直流電流Idcとキャパシタバンクの端子電圧 inの2次元座標面に対する第3次軸に対してプロットしたものである。

[0044]

直流電流の増加に伴ってスイッチング損失が増大し、変換効率が低下していることが確認できる。

さらに、ハードスイッチングとソフトスイッチングで比較すると、ソフトスイッチングの第3次軸における目盛りが著しく細かくプロットされていることに注意すれば、ソフトスイッチングにおけるエネルギ損失がいずれの領域においても著しく小さく、変換効率が著しく大きいことが理解できる。

[0045]

なお、上記実施例では、電力貯蔵要素として電気二重層キャパシタを利用したが、通常の大容量キャパシタや二次電池を利用してもよい。

また、本実施例の双方向DC-DCコンバータは電流形インバータと組み合わせて電力 貯蔵装置を構成して交流機器の駆動に使用したが、直流機器に適用することができること はいうまでもない。

なお、上記実施例は本願発明を実施するための最良の形態を示したものに過ぎず、本明

20

10

30

40

細書に説明した技術的思想および特許請求の範囲の記載に基づいていわゆる当業者が想到 する他の装置および方法に対しても本願発明の技術範囲に属することはいうまでもない。

## 【図面の簡単な説明】

- [0046]

- 【図1】本発明の1実施例に係る双方向DC-DCコンバータのソフトスイッチング回路を用いた電流形電力貯蔵装置の主回路構成図である。

- 【図2】本実施例の双方向DC-DCコンバータの充電時の等価回路図である。

- 【図3】本実施例の双方向DC-DCコンバータの放電時の等価回路図である。

- 【図4】本実施例の双方向 D C D C コンバータの充電時におけるモード別の等価回路図である。

- 【図5】シミュレーションにより得られた本実施例における各部の瞬時電圧・電流の波形図である。

- 【図 6 】シミュレーションにより得られたハードスイッチング手法による各部の瞬時電圧 ・電流の波形図である。

- 【図7】GTOサイリスタの等価回路図である。

- 【図8】シミュレーションに用いたパラメータの表である。

- 【図9】共振用キャパシタパラメータの決定条件を表すグラフである。

- 【図10】本実施例の双方向DC-DCコンバータのソフトスイッチングにおけるエネルギ損失を表すグラフである。

- 【図11】本実施例の双方向DC-DCコンバータのソフトスイッチングにおける変換効率を表すグラフである。

- 【図12】本実施例の双方向DC-DCコンバータの等価物についてハードスイッチング したときのエネルギ損失を表すグラフである。

- 【図13】本実施例の双方向DC-DCコンバータの等価物についてハードスイッチング したときの変換効率を表すグラフである。

# 【符号の説明】

## [0047]

- 1 直流電源

- 2 双方向 D C D C コンバータ

- 3 電流形インバータ3

- 4 誘導電動機

- 5 直流インダクタ

- 6 交流フィルタ

20

10

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

# 【図7】

# 【図8】

表 シミュレーションパラメータ

| GTOサイリスタ   |               |                           |

|------------|---------------|---------------------------|

| 内部抵抗       | Ron           | $\operatorname{lm}\Omega$ |

| 内部インダクタンス  | Lon           | 1 μ Η                     |

| 順方向電圧      | Vf            | 1V                        |

| 急速回復用ダイオード |               |                           |

| 内部抵抗       | Ron           | $1 \text{m}  \Omega$      |

| 内部インダクタンス  | Lon           | $1~\mu$ H                 |

| 順方向電圧      | Vf            | 0.87                      |

| 入力電圧       | Vin           | 190V                      |

| 直流インダクタ    | Ldc           | 1 mH                      |

| 第1共振用インダクタ | Lrl           | 0.5 μ Η                   |

| 第2共振用インダクタ | Lr2           | $1~\mu$ H                 |

| 共振用キャパシタ   | $C\mathbf{r}$ | 80 μ F                    |

| スイッチング周波数  | fsbo          | 10kHz=1/100 μ s           |

| デューティ      | d             | 50%                       |

| フィルタ用インダクタ | Lac           | 0. 1mH                    |

| フィルタ用キャパシタ | Cac           | 5 μ F                     |

# 【図9】

【図10】

【図11】

【図13】

【図12】

# フロントページの続き

(56)参考文献 特開平11-008096(JP,A)

特開平02-074124(JP,A)

特開2002-078323(JP,A)

特開平02-211054(JP,A)

特開2003-250267(JP,A)

特開昭60-249871(JP,A)

特開2003-088107(JP,A)

(58)調査した分野(Int.CI., DB名)

H 0 2 M 3 / 1 3 5