## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2019-71604 (P2019-71604A)

(43) 公開日 令和1年5月9日(2019.5.9)

(51) Int. Cl. FLテーマコード (参考) нозм 1/50 (2006, 01) нозм 5J022 1/50 нозк 5/153 (2006, 01) нозк 5/153 51039 Α

# 審査請求 未請求 請求項の数 10 OL (全 23 頁)

| (21) 出願番号<br>(22) 出願日 | 特願2018-159235 (P2018-159235)<br>平成30年8月28日 (2018.8.28) | (71) 出願人 | 504258527<br>国立大学法人 鹿児島大学 |

|-----------------------|--------------------------------------------------------|----------|---------------------------|

| (31) 優先権主張番号          | 特願2017-197050 (P2017-197050)                           |          | 鹿児島県鹿児島市郡元一丁目21番24号       |

| (32) 優先日              | 平成29年10月10日 (2017.10.10)                               | (74)代理人  | 100095407                 |

| (33) 優先権主張国           | 日本国(JP)                                                |          | 弁理士 木村 満                  |

|                       | · ·                                                    | (74)代理人  | 100162259                 |

|                       |                                                        |          | 弁理士 末富 孝典                 |

|                       |                                                        | (74)代理人  | 100133592                 |

|                       |                                                        |          | 弁理士 山口 浩一                 |

|                       |                                                        | (74)代理人  | 100168114                 |

|                       |                                                        |          | 弁理士 山中 生太                 |

|                       |                                                        | (72) 発明者 | 大畠 賢一                     |

|                       |                                                        |          | 鹿児島県鹿児島市郡元一丁目21番24号       |

|                       |                                                        |          | 国立大学法人 鹿児島大学内             |

|                       |                                                        | Fターム (参  | 考) 5J022 AA11 CF02        |

|                       |                                                        | ' '-     | 5J039 DA01                |

## (54) 【発明の名称】電圧・時間変換器及びアナログ・デジタル変換器

# (57)【要約】

【課題】良好な線形性を得ることができる電圧・時間変換器を提供する。また、変換精度を上げても消費電力の増加、動作速度の低下を抑制することができるアナログ・デジタル変換器を提供する。

【解決手段】電圧・時間変換器 1 A は、差動電圧信号( $V_{i \text{ n p}}$  、 $V_{i \text{ n n}}$  )を時間出力に変換する。変換回路 2 0 は、差動電圧信号( $V_{i \text{ n p}}$  、 $V_{i \text{ n n}}$  )をゲート電圧として入力し、差動電圧信号( $V_{i \text{ n p}}$  、 $V_{i \text{ n n}}$  )の大きさに応じた時間出力を示すタイミング信号(S T A R T ,S T O P )に線形変換する第 1 の M O S 差動回路を備える。歪み補正回路 3 0 は、差動電圧信号( $V_{i \text{ n p}}$  、 $V_{i \text{ n n}}$  )からタイミング信号(S T A R T ,S T O P )への線形変換が線形性を保つように、第 1 の M O S 差動回路から出力されタイミング信号(S T A R T ,S T O P )に対応する一対の電流を補正する。

【選択図】図1

#### 【特許請求の範囲】

## 【請求項1】

差動電圧信号をゲート電圧として入力し、該差動電圧信号の大きさに応じた時間出力を示す一対のパルス電圧信号に変換する第1のMOS差動回路を備える変換回路と、

前記変換回路における前記差動電圧信号から前記一対のパルス電圧信号への変換が線形性を保つように、前記一対のパルス電圧信号に対応する電流として前記第1のMOS差動回路から出力される一対の電流を補正する補正回路と、

を備える電圧・時間変換器。

## 【請求項2】

前記補正回路は、

前記一対の電流にそれぞれ補正電流を加えることにより、前記一対のパルス電圧信号に含まれる前記差動電圧信号の高次成分を除去する第2のMOS差動回路を備える歪み補正回路である、

請求項1に記載の電圧・時間変換器。

# 【請求項3】

前記第1のMOS差動回路と前記第2のMOS差動回路とで、入力する前記差動電圧信号の極性が逆であり、

前記第1のMOS差動回路において前記差動電圧信号を入力するCMOSの利得係数と、前記第2のMOS差動回路において前記差動電圧信号を入力するCMOSの利得係数。との関係が、

c = (3 - 2 2)

を満たす、

請求項2に記載の電圧・時間変換器。

#### 【請求項4】

前記第2のMOS差動回路に入力する2つのゲート電圧を一定の電圧とし、 前記第1のMOS差動回路において前記差動電圧信号を入力するCMOSの利得係数

前記第 2 の M O S 差動回路において前記 2 つのゲート電圧を入力する C M O S の利得係数 。との関係が、

\_ =

を満たし、

前記第1のMOS差動回路に入力される前記差動電圧信号のコモンレベルV<sub>с。m</sub>と、前記第2のMOS差動回路に入力される前記2つのゲート電圧のコモンレベルV<sub>c</sub>との関係が、

$V_{com} = V_{c}$

を満たす、

請求項2に記載の電圧・時間変換器。

## 【請求項5】

前記第2のMOS差動回路へ入力される前記2つのゲート電圧の正側電圧と負側電圧との間に、前記一対のパルス電圧信号に含まれるオフセット成分を打ち消すオフセットを与える、

請求項4に記載の電圧・時間変換器。

## 【請求項6】

前記変換回路は、

前記第1のMOS差動回路に一対の抵抗を挿入することにより、前記差動電圧信号に比例して増加する前記一対の電流を出力し、

前記補正回路は、

前記一対の電流にそれぞれ補正電流を加えることにより、前記差動電圧信号と前記一対のパルス電圧信号に対応する電流との伝達関数を、理想的な伝達関数に折れ線近似する、請求項1に記載の電圧・時間変換器。

10

20

30

40

#### 【請求項7】

前記補正回路は、

前記差動電圧信号をゲート電圧として入力し、一対の抵抗が挿入され、前記差動電圧信号に比例して増加する前記補正電流を出力する少なくとも1つの第3のMOS差動回路を備える、

請求項6に記載の電圧・時間変換器。

#### 【請求項8】

前記補正回路は、

一定の電圧をゲート電圧として入力し、一定の電流を前記補正電流として出力する第 4 の M O S 差動回路を備える、

請求項6に記載の電圧・時間変換器。

## 【請求項9】

ゲート電圧を入力する一対のСМОЅのソース端子が分離されて、各々のソース端子に クロック信号により制御される別のСМОЅが接続されている、

請求項1から8のいずれか一項に記載の電圧・時間変換器。

#### 【請求項10】

入力した差動電圧信号を、n(nは自然数)ビットのデジタル信号のうちの上位m(mはnより少ない自然数)ビットの上位デジタル信号に変換する上位AD変換器と、

前記差動電圧信号と、前記上位AD変換器から出力された上位デジタル信号とに基づいて、前記差動電圧信号の残差信号を発生させる残差発生回路と、

前記残差信号を、 n ビットのデジタル信号のうちの下位 n - m ビットの下位デジタル信号に変換する下位 A D 変換器と、

前記上位デジタル信号と、前記下位デジタル信号とを合成して、 n ビットのデジタル信号として出力する合成器と、

を備え、

前記上位AD変換器及び前記下位AD変換器の少なくとも一方が、請求項1から9のいずれか一項に記載の電圧・時間変換器を備えている、

アナログ・デジタル変換器。

【発明の詳細な説明】

## 【技術分野】

[0001]

本発明は、電圧・時間変換器及びアナログ・デジタル変換器に関する。

#### 【背景技術】

# [0002]

CMOS(Complementary Metal Oxide Semiconductor)の微細化に伴い、デジタル回路の性能向上はめざましく、小面積化、高速化、低電力化が進んでいる。アナログ回路においても、微細化による遮断周波数の向上により、ミリ波やテラHz領域で動作可能なLSI(Large-Scale Integration)が登場している。しかしながら、その反面、真性利得の低下、素子ばらつきの増大、電源電圧低下に伴うSN比の劣化など、微細化の負の側面も顕在化しており、これを解決する様々な技術が検討されている。

[0003]

その中で最近、信号を時間領域で表現して処理する時間領域アナログ技術が注目を集めている。時間領域で信号を表現すれば、電源電圧に制限されない信号表現が可能となり、デジタル回路中心の回路構成が可能となるため、微細化の恩恵を享受しやすい。

### [0004]

こうした背景の下、時間領域アナログ技術を用いたアナログ・デジタル変換器(Analog -to-Digital Converter; ADC)の研究も盛んに行われている。例えば非特許文献 1 では、電圧・時間変換器(Voltage-to-Time Converter; VTC)と時間・デジタル変換器(Time-to-Digital Converter; TDC)を組み合わせたアナログ・デジタル変換器が報告されている。このアナログ・デジタル変換器では、入力した差動電圧信号が、電圧・時間変換器で時

10

20

30

40

間出力に変換された後、時間・デジタル変換器において時間出力がデジタル信号へ変換される。

## [0005]

時間・デジタル変換器としては高速化に適した並列型が採用されており、並列型の時間・デジタル変換器では、5GHzの高速動作が170fJ/conv.-stepという低エネルギーで実現されている。また、従来の電圧領域のアナログ・デジタル変換器と時間領域のアナログ・デジタル変換器を組み合わせる試みも報告されている(非特許文献2参照)。この組み合わせでは、逐次変換型(Successive Approximations Register; SAR)アナログ・デジタル変換器で粗い変換が行われた後に、入力した差動電圧信号と粗い変換結果との残差信号が、時間領域のアナログ・デジタル変換器でデジタル信号に変換される。これにより、動作速度は250kHzと低速ではあるが、2.02fJ/conv.-stepという極低エネルギー動作を可能とするアナログ・デジタル変換器が実現されている。

【先行技術文献】

## 【非特許文献】

#### [0006]

【非特許文献 1】Yongsheng Xu, et al., "5-bit 5-GS/s Noninterleaved Time-Based A DC in 65-nm CMOS for Radio-Astronomy Applications, "IEEE Transactions on Very L arge Scale Integration(VLSI) Systems, vol.24, no.12, pp.3513-3525, Dec.2016.

【非特許文献 2】Yan-Jiun Chen, et al., "A 2.02-5.16 fJ/Conversion Step 10 Bit Hybrid Coarse-Fine SAR ADC With Time-Domain Quantizer in 90nm CMOS," IEEE Journa I of Solid-State Circuits, vol.51, no.2, pp.357-364, Feb. 2016.

#### 【発明の概要】

【発明が解決しようとする課題】

#### [0007]

非特許文献1のアナログ・デジタル変換器は、電圧・時間変換器を用いて、入力した差動電圧信号を時間出力に変換した後に、時間・デジタル変換器を用いて、時間出力をデジタル信号へ変換する。しかしながら、この電圧・時間変換器の線形性には限界があるため、変換精度は5ビットに留まっている。また、仮に電圧・時間変換器の線形性の問題が解決できたとしても、時間・デジタル変換器が並列型であるため、変換精度を上げると回路規模と変換時間が指数関数的に増加してしまい、消費電力の増加、動作速度の低下の問題に直面する。

### [0008]

本発明は、上記実情に鑑みてなされたものであり、良好な線形性を得ることができる電圧・時間変換器を提供することを目的とする。また、本発明は、変換精度を上げても消費電力の増加、動作速度の低下を抑制することができるアナログ・デジタル変換器を提供することを目的とする。

【課題を解決するための手段】

# [0009]

本発明の第1の観点に係る電圧・時間変換器は、

差動電圧信号をゲート電圧として入力し、該差動電圧信号の大きさに応じた時間出力を示す一対のパルス電圧信号に変換する第1のMOS差動回路を備える変換回路と、

前記変換回路における前記差動電圧信号から前記一対のパルス電圧信号への変換が線形性を保つように、前記一対のパルス電圧信号に対応する電流として前記第1のMOS差動回路から出力される一対の電流を補正する補正回路と、

を備える。

# [0010]

この場合、前記補正回路は、

前記一対の電流にそれぞれ補正電流を加えることにより、前記一対のパルス電圧信号に含まれる前記差動電圧信号の高次成分を除去する第2のMOS差動回路を備える歪み補正

10

20

30

40

回路である、

こととしてもよい。

### [0011]

また、前記第1のMOS差動回路と前記第2のMOS差動回路とで、入力する前記差動電圧信号の極性が逆であり、

前記第1のMOS差動回路において前記差動電圧信号を入力するCMOSの利得係数と、前記第2のMOS差動回路において前記差動電圧信号を入力するCMOSの利得係数。との関係が、

( = ( 3 - 2 2 )

を満たす、

こととしてもよい。

[0012]

また、前記第2のMOS差動回路に入力する2つのゲート電圧を一定の電圧とし、 前記第1のMOS差動回路において前記差動電圧信号を入力するCMOSの利得係数 と、

前記第2のMOS差動回路において前記2つのゲート電圧を入力するCMOSの利得係数 。との関係が、

<sub>c</sub> =

を満たし、

前記第1のMOS差動回路に入力される前記差動電圧信号のコモンレベルV 。。m と、前記第2のMOS差動回路に入力される前記2つのゲート電圧のコモンレベルV 。との関係が、

$V_{com} = V_{c}$

を満たす、

こととしてもよい。

[0013]

前記第2のMOS差動回路へ入力される前記2つのゲート電圧の正側電圧と負側電圧との間に、前記一対のパルス電圧信号に含まれるオフセット成分を打ち消すオフセットを与える、

こととしてもよい。

[ 0 0 1 4 ]

前記変換回路は、

前記第1のMOS差動回路に一対の抵抗を挿入することにより、前記差動電圧信号に比例して増加する前記一対の電流を出力し、

前記補正回路は、

前記一対の電流にそれぞれ補正電流を加えることにより、前記差動電圧信号と前記一対のパルス電圧信号に対応する電流との伝達関数を、理想的な伝達関数に折れ線近似する、こととしてもよい。

[0015]

前記補正回路は、

前記差動電圧信号をゲート電圧として入力し、一対の抵抗が挿入され、前記差動電圧信号に比例して増加する前記補正電流を出力する少なくとも 1 つの第 3 の M O S 差動回路を備える、

こととしてもよい。

[0016]

前記補正回路は、

一定の電圧をゲート電圧として入力し、一定の電流を前記補正電流として出力する第 4 の M O S 差動回路を備える、

こととしてもよい。

[0017]

10

20

30

40

ゲート電圧を入力する一対のCMOSのソース端子が分離されて、各々のソース端子に クロック信号により制御される別のCMOSが接続されている、

こととしてもよい。

[ 0 0 1 8 ]

本発明の第2の観点に係るアナログ・デジタル変換器は、

入力した差動電圧信号を、n(nは自然数)ビットのデジタル信号のうちの上位m(mはnより少ない自然数)ビットの上位デジタル信号に変換する上位AD変換器と、

前記差動電圧信号と、前記上位AD変換器から出力された上位デジタル信号とに基づいて、前記差動電圧信号の残差信号を発生させる残差発生回路と、

前記残差信号を、 n ビットのデジタル信号のうちの下位 n - m ビットの下位デジタル信号に変換する下位 A D 変換器と、

前記上位デジタル信号と、前記下位デジタル信号とを合成して、 n ビットのデジタル信号として出力する合成器と、

を備え、

前記上位AD変換器及び前記下位AD変換器の少なくとも一方が、本発明の第1の観点に係る電圧・時間変換器を備えている。

【発明の効果】

[0019]

本発明によれば、差動電圧信号を時間出力に変換する場合に、その線形性を保つために一対のパルス電圧信号に対応する一対の電流を補正するので、良好な線形性を得ることができる。また、本発明によれば、一度に変換するデジタル信号のビット数を少なくすることができるので、変換精度を上げても消費電力の増加、動作速度の低下を抑制することができる。

【図面の簡単な説明】

[0020]

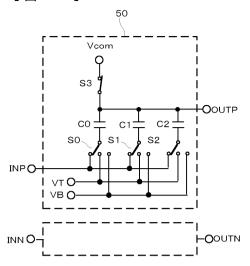

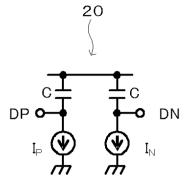

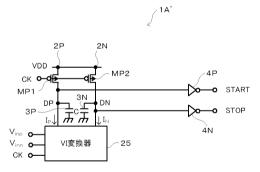

- 【図1】本発明の実施の形態1に係る電圧・時間変換器の回路図である。

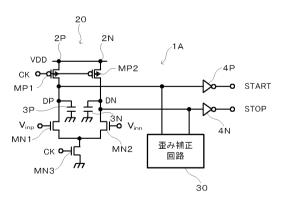

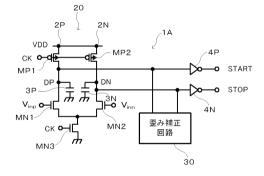

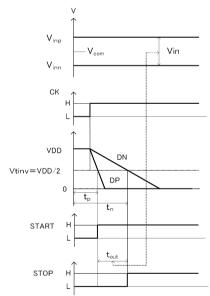

- 【図2】図1の電圧・時間変換器の動作を示すタイミングチャートである。

- 【図3】図1の電圧・時間変換器の等価回路図である。

- 【図4】歪み補正回路の構成を示す回路図である。

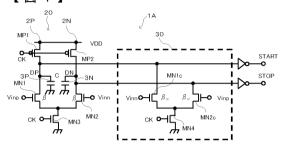

- 【図5】本発明の実施の形態2に係る電圧・時間変換器の回路図である。

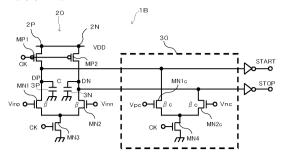

- 【図6】本発明の実施の形態3に係る電圧・時間変換器の回路図である。

- 【図7】従来の電圧・時間変換器の回路図である。

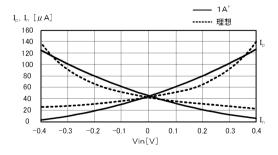

- 【図8】従来の電圧・時間変換器における差動電圧と電流との伝達関数を示す図である。

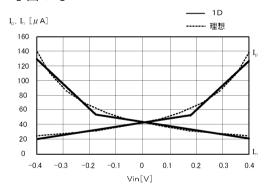

- 【図9】折れ線状の近似伝達関数を示す図である。

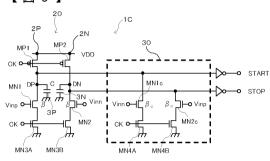

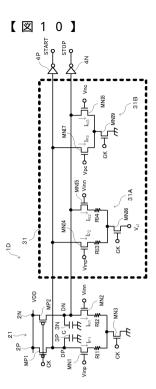

- 【図10】本発明の実施の形態4に係る電圧・時間変換器の回路図である。

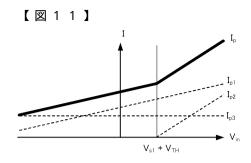

- 【図11】本発明の実施の形態4に係る電圧・時間変換器における差動電圧と電流との伝達関数を示す図である。

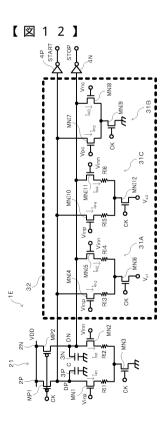

- 【図12】本発明の実施の形態5に係る電圧・時間変換器の回路図である。

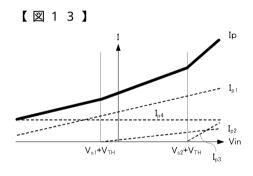

- 【図13】本発明の実施の形態5に係る電圧・時間変換器における差動電圧と電流との伝達関数を示す図である。

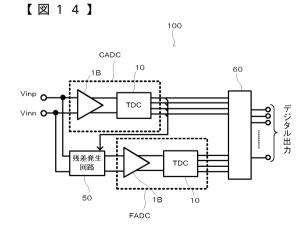

- 【図14】本発明の実施の形態6に係るアナログ・デジタル変換器の回路図である。

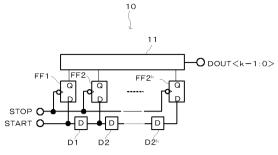

- 【図15】時間・デジタル変換器の回路構成の一例を示す回路図である。

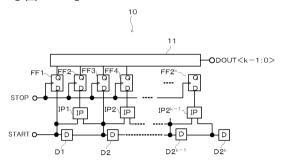

- 【図16】時間・デジタル変換器の回路構成の他の例を示す回路図である。

- 【図17】残差発生回路の回路構成の一例を示す回路図である。

【発明を実施するための形態】

[0021]

以下、本発明の実施の形態について図面を参照して詳細に説明する。

[0022]

実施の形態1.

まず、本発明の実施の形態1について説明する。

30

10

20

40

#### [ 0 0 2 3 ]

本実施の形態に係る電圧・時間変換器 1 A(図 1 参照)は、差動電圧信号をその大きさに応じた時間出力に線形変換する。本実施の形態では、図 2 に示すように、入力する差動電圧信号の正側電圧信号を  $V_{inp}$  とし、負側電圧信号を  $V_{inn}$  とし、差動電圧信号を  $(V_{inp}, V_{inn})$  で表す。差動電圧は  $V_{in}$  となる。また、電圧・時間変換器 1 Aから出力される一対のパルス電圧信号、すなわちタイミング信号を(START信号,STOP信号)とする。START信号とSTOP信号との立ち上がりの時間差を時間出力 t0 。 t1 とする。

# [0024]

時間出力 t 。 u t は、START信号がローレベルからハイレベルに移行した時点から、STOP信号がローレベルからハイレベルに移行した時点との間の時間を示す。以下では、2値信号における下側のレベル、すなわちローレベルを "L"とし、上側のレベル、すなわちハイレベルを "H"と表す。

## [0025]

図1に示すように、この電圧・時間変換器1Aは、変換回路20と、補正回路としての歪み補正回路30と、を備える。変換回路20は、差動電圧信号(V<sub>inp</sub>,V<sub>inn</sub>)を入力し、該差動電圧信号(V<sub>inp</sub>,V<sub>inn</sub>)をその大きさに応じた時間出力t<sub>。ut</sub>を示すタイミング信号を(START信号,STOP信号)に変換する第1のMOS差動回路を備える。

# [0026]

第1のMOS差動回路は、START信号を出力するためのMOSトランジスタ(CMOS)MP1,MN1と、STOP信号を出力するためのMOSトランジスタMP2,MN2と、両信号に共通のMOSトランジスタMN3と、電源電圧端子2P,2Nと、ノードDP,DNと、コンデンサ3P,3Nと、を備える。この他、変換回路20は、インバータ4P,4Nを備える。

# [0027]

第1のMOS差動回路は、正側電圧信号Vinpを入力するMOSトランジスタMN1と、負側電圧信号Vinnを入力するMOSトランジスタMN2と、を中心に構成される。なお、MOSトランジスタMN1,MN2の電子の移動度をμとし、単位面積当たりのゲート容量をCoxとし、MOSのゲート幅をwとし、ゲート長をLとすると、MOSトランジスタMN1、MOSトランジスタMN2の利得係数 は、以下の式で表される。

= μ · C o x · ( w / L ) ... ( 1 )

#### [0028]

MOSトランジスタMN1は、電源電圧VDDを供給する電源電圧端子2Pと、グラウンドとの間に挿入されている。MOSトランジスタMN1は、正側電圧信号V<sub>inp</sub>を、ゲート電圧(制御電圧)として入力する。MOSトランジスタMN1とグラウンドとの間には、クロック信号CKをゲート電圧として入力するMOSトランジスタ(スイッチ)MN3が挿入されている。

## [0029]

また、MOSトランジスタMN1と電源電圧端子2Pとの間には、クロック信号CKの反転信号をゲート電圧として入力するMOSトランジスタ(スイッチ)MP1が挿入されている。MOSトランジスタMP1とMOSトランジスタMN1との間に、ノードDPが形成されている。ノードDPは、コンデンサ3Pを介して接地されている。また、ノードDPは、インバータ4Pと接続されている。インバータ4Pの出力がSTART信号となる。

# [0030]

一方、MOSトランジスタMN2は、電源電圧VDDを供給する電源電圧端子2Nと、グラウンドとの間に挿入されている。MOSトランジスタMN2は、負側電圧信号Vin を、ゲート電圧(制御電圧)として入力する。MOSトランジスタMN2とグラウンドとの間には、クロック信号CKをゲート電圧として入力するMOSトランジスタ(スイッ

10

20

30

00

40

10

20

30

50

チ) M N 3 が挿入されている。

[0031]

MOSトランジスタMN2と電源電圧端子2Nとの間には、クロック信号CKの反転信号をゲート電圧として入力するMOSトランジスタMP2(スイッチ)が挿入されている。MOSトランジスタMP2とMOSトランジスタMN2との間に、ノードDNが形成されている。ノードDNは、コンデンサ3Nを介して接地されている。また、ノードDNは、インバータ4Nと接続されている。インバータ4Nの出力がSTOP信号となる。

[0032]

この電圧・時間変換器1Aは、クロック信号CKに従って動作する。クロック信号CKは、一定周期で"L"と"H"とを繰り返す信号である。クロック信号CKが"L"となっている期間を、プリチャージ期間とし、クロック信号CKが"H"となっている期間を、変換期間とする。

[0033]

図 2 に示すように、プリチャージ期間では、クロック信号 C K が " L "となっているので、M O S トランジスタ M N 3 がオフとなり、M O S トランジスタ M P 1 , M P 2 がオンとなる。このため、コンデンサ 3 P , 3 N が蓄電されて、ノード D P , D N の電圧が電源電圧 V D D となっている。

[0034]

その後、プリチャージ期間から変換期間に移行すると、クロック信号 C K が " H " に切り替わるので、M O S トランジスタ M N 3 がオンとなり、 M O S トランジスタ M P 1 , M P 2 がオフとなる。このため、差動電圧信号( V <sub>i n p</sub> , V <sub>i n n</sub> )に依存した電流( I <sub>p</sub> , I <sub>n</sub> )が M O S トランジスタ M N 1 , M N 2 に流れてノード D P , D N が放電される。

[0035]

ノードDP,DNの電位がインバータ4P,4Nのしきい値電圧Vtinvを下回ると、その時刻にSTART信号,STOP信号が立ち上がる。START信号,STOP信号の立ち上がりの時間差が時間出力  $t_{out}$ となる。ノードDP,DNの放電時間は、差動電圧信号(V $_{inp}$ ,V $_{inn}$ )に依存して変化し、差動電圧信号(V $_{inp}$ ,V $_{inn}$ )が小さい範囲ではSTART信号,STOP信号で規定される時間出力  $t_{out}$ は、差動電圧V $_{inn}$ に比例することから、この回路は電圧・時間変換回路として機能する。

[0036]

図 3 に示すように、 M O S トランジスタ M N 1 , M N 2 を備える電圧・時間変換器 1 A は、容量 C に蓄えられた電荷を放電する定電流(  $I_p$  ,  $I_n$  )の電流源回路でモデル化される。ここで、 図 2 に示すように、差動電圧信号(  $V_{inp}$  ,  $V_{inn}$  )のコモンレベルを  $V_{com}$  とし、定電流(信号電流)(  $I_p$  ,  $I_n$  )は以下の式( 2 )で表せるものと近似する。

[ 0 0 3 7 ]

【数1】

$$I_{P} = \frac{\beta}{2} \left( V_{com} + \frac{V_{in}}{2} - V_{TH} \right)^{2}$$

$$I_{N} = \frac{\beta}{2} \left( V_{com} - \frac{V_{in}}{2} - V_{TH} \right)^{2}$$

$$\qquad (2)$$

ここで、 $V_{TH}$ は、MOSトランジスタMN1, MN2のしきい値電圧である。ノードDP, DNがインバータ4P, 4Nのしきい値VtinVを下回るまでの時間 tp, tnは、以下の式(3)で表せる。

【 0 0 3 8 】 【数 2 】

$$t_{p} = \frac{CV_{DD}}{2I_{p}}$$

$$t_{n} = \frac{CV_{DD}}{2I_{n}}$$

... (3)

10

ただし、ここで、V t i n V = V D D / 2 とした。式( 2 )、式( 3 )から時間出力 t 。  $_{\rm out}$  を求めると、以下の式のようになる。

[0039]

【数3】

$$t_{out} = \frac{32CV_{DD}V_{in}(V_{com} - V_{TH})}{\beta \left[V_{in}^{2} - 4(V_{com} - V_{TH})^{2}\right]^{2}}$$

$$\approx \frac{2CV_{DD}}{\beta (V_{com} - V_{TH})^{3}}V_{in} + \frac{CV_{DD}}{\beta (V_{com} - V_{TH})^{5}}V_{in}^{3} + \frac{3CV_{DD}}{8\beta (V_{com} - V_{TH})^{7}}V_{in}^{5}$$

$$= GV_{in} + \frac{G}{2(V_{com} - V_{TH})^{2}}V_{in}^{3} + \frac{3G}{8(V_{com} - V_{TH})^{4}}V_{in}^{5} \cdots (4)$$

ここで、 G は電圧・時間変換器の利得である。この式( 4 )からわかるように、変換回路 2 0 は、( V  $_{\rm com}$  - V  $_{\rm TH}$  )  $^3$  に反比例する 3 次成分の歪( 3 次歪)を発生する。

[0040]

30

補正回路としての歪み補正回路 3 0 は、信号電流( $I_p$ ,  $I_n$ ) に補正電流( $I_{pc}$ ,  $I_{nc}$ ) を加えることにより、上述の 3 次歪を打ち消し、時間出力  $t_{out}$ の線形性を改善する。歪み補正回路 3 0 は、変換回路 2 0 における差動電圧信号( $V_{inp}$ ,  $V_{inn}$ ) からタイミング信号(START信号,STOP信号)への線形変換が線形性を保つように、タイミング信号(START信号,STOP信号)に対応する電流として第 1 の MOS を動回路から出力される一対の電流( $I_p$ ,  $I_N$ )を補正する。

[0041]

[0042]

50

50

補正電流( $I_{pc}$ ,  $I_{nc}$ )は以下の式(5)で表される。歪み補正回路 3 0 では、入力信号の接続を、上述のように変換回路 2 0 と入れ替えている(極性を逆にしている)ため、式(5)と式(2)とでは差動電圧  $V_{in}$ の符号が反転している。

[0043]

【数4】

$$I_{pc} = \frac{\beta_c}{2} \left( V_{com} - \frac{V_{in}}{2} + V_{TH} \right)^2$$

$$I_{nc} = \frac{\beta_c}{2} \left( V_{com} + \frac{V_{in}}{2} - V_{TH} \right)^2$$

10

この回路の時間出力  $t_{out}$  を求めると、以下の式(6)のようになる。  $_c$  は、MOSトランジスタMN1 c , MN2 c の利得係数である。

[0044]

【数5】

$$t_{out} \approx \frac{2CV_{DD}(\beta - \beta_c)}{(\beta + \beta_c)^2 (V_{com} - V_{TH})^3} V_{in} + \frac{CV_{DD}(\beta - \beta_c)(\beta^2 - 6\beta\beta_c + \beta_c^2)}{(\beta + \beta_c)^4 (V_{com} - V_{TH})^5} V_{in}^3 + \frac{CV_{DD}(\beta - 3\beta_c)(\beta - \beta_c)(3\beta - \beta_c)(\beta^2 - 14\beta\beta_c + \beta_c^2)}{8(\beta + \beta_c)^6 (V_{com} - V_{TH})^7} V_{in}^5 \cdots (6)$$

ここで、利得Gを以下の式(7)のように定義する。

[0045]

【数6】

$$G = \frac{2CV_{DD}(\beta - \beta_c)}{(\beta + \beta_c)^2 (V_{com} - V_{TH})^3} \cdots (7)$$

時間出力 t 。 u t は、以下の式(8)のようになる。

[0046]

【数7】

$$t_{out} \approx GV_{in} + \frac{G(\beta^{2} - 6\beta\beta_{c} + \beta_{c}^{2})}{2(\beta + \beta_{c})^{2}(V_{com} - V_{TH})^{2}}V_{in}^{3} + \frac{G(\beta - 3\beta_{c})(3\beta - \beta_{c})(\beta^{2} - 14\beta\beta_{c} + \beta_{c}^{2})}{16(\beta + \beta_{c})^{6}(V_{com} - V_{TH})^{4}}V_{in}^{5} \cdots (8)$$

上記式(8)では、第2項が、3次歪に対応する。この式(8)からわかるように、第2項において、(V $_{\rm com}$ -V $_{\rm TH}$ ) $^2$ に反比例する3次歪みが発生する。

[0047]

ここで、第1のMOS差動回路において差動電圧信号(Vinp,Vinn)を入力す

20

40

50

る M O S トランジスタ M N 1 , M N 2 の利得係数 と、第 2 の M O S 差動回路において差動電圧信号(  $V_{inp}$  ,  $V_{inn}$  )を入力する M O S トランジスタ M N 1 c , M N 2 c の利得係数 。との関係が、 。=(3-2-2) を満たすとすると、式( 8 )の第 2 項は 0 となり 3 次歪をキャンセルすることができる。この場合の時間出力 t 。 ut 、以下のようになる。

[0048]

【数8】

$$t_{out} \approx GV_{in} - \frac{G}{16(V_{com} - V_{TH})^4} V_{in}^5 \quad \cdots \quad (9)$$

3次歪がキャンセルされることで、従来の電圧・時間変換器と比較した場合、線形性を 大きく改善することができる。

[0049]

実施の形態2.

次に、本発明の実施の形態2について説明する。

[0050]

本実施の形態に係る電圧・時間変換器1Bは、変換回路20と歪み補正回路30とを備える点では、上記実施の形態1に係る電圧・時間変換器1Aと同じである。本実施の形態に係る電圧・時間変換器1Bは、歪み補正回路30において、第2のMOS差動回路を構成するMOSトランジスタMN1c,MN2cに入力されるゲート電圧(制御電圧)が、上記実施の形態1と異なっている。

[0051]

図 5 に示すように、本実施の形態では、M O S トランジスタ M N 1 c , M N 2 c に入力されるゲート電圧を一定の電圧( $V_{pc}$ ,  $V_{nc}$ )としている。補正電流( $I_{pc}$ ,  $I_{nc}$ )は、制御電圧  $V_{pc}$ ,  $V_{nc}$ を印加した第 2 の M O S 差動回路により生成する。この場合、補正電流  $I_{pc}$ ,  $I_{nc}$ は、以下の式で表せる。

[0052]

【数9】

$$I_{pc} = \frac{\beta_{c}}{2} (V_{pc} - V_{TH})^{2}$$

$$I_{nc} = \frac{\beta_{c}}{2} (V_{nc} - V_{TH})^{2}$$

... (10)

ここから、時間出力 t  $_{out}$  を求めると、以下の式となる。ただし、 V  $_{pc}$  = V  $_{nc}$  = V  $_{c}$  としている。

[0053]

【数10】

$$\begin{split} &t_{out} \approx \frac{2CV_{DD}(V_{com} - V_{TH}) \ \beta}{\left[ (V_{com} - V_{TH})^2 \beta + \ (V_c - V_{TH})^2 \beta_c \ \right]^2} V_{in} \\ &+ \frac{CV_{DD}(V_{com} - V_{TH})^2 \beta^2 \left[ (V_{com} - V_{TH})^2 \beta - (V_c - V_{TH})^2 \beta_c \right]}{\left[ (V_{com} - V_{TH})^2 \beta + \ (V_c - V_{TH})^2 \beta_c \ \right]^4} \\ &+ \frac{CV_{DD}(V_{com} - V_{TH}) \ \beta^3 \left[ 3 \ (V_{com} - V_{TH})^4 \beta^2 - 10(V_c - V_{TH})^2 (V_{com} - V_{TH})^2 \beta \beta_c + 3(V_c - V_{TH})^4 \beta_c^2 \right]}{8 \left[ (V_{com} - V_{TH})^2 \beta + (V_c - V_{TH})^2 \beta_c \right]^6} \dots \ (11) \end{split}$$

ここで、利得Gを以下のように定義すると、

[0054]

【数11】

$$G = \frac{2CV_{DD}(V_{com} - V_{TH})\beta}{(V_{com} - V_{TH})^2 \beta + (V_c - V_{TH})^2 \beta_c} \cdots (12)$$

時間出力t。utは、以下のように表せる。

[ 0 0 5 5 ]

【数12】

$$\begin{split} t_{\text{out}} &\approx G V_{\text{in}} + \frac{G \beta \left[ (V_{\text{com}} - V_{\text{TH}})^2 \beta - (V_c - V_{\text{TH}})^2 \beta_c \right]}{2 \left[ (V_{\text{com}} - V_{\text{TH}})^2 \beta + (V_c - V_{\text{TH}})^2 \beta_c \right]^2} V_{\text{in}}^3 \\ &+ \frac{G \beta^2 \left[ 3 - (V_{\text{com}} - V_{\text{TH}})^4 \beta^2 - 10(V_c - V_{\text{TH}})^2 (V_{\text{com}} - V_{\text{TH}})^2 \beta \beta_c + 3(V_c - V_{\text{TH}})^4 \beta_c^2 \right]}{16 \left[ (V_{\text{com}} - V_{\text{TH}})^2 \beta + (V_c - V_{\text{TH}})^2 \beta_c \right]^4} V_{\text{in}}^5 \cdots (13) \end{split}$$

ここで、第1のMOS差動回路において差動電圧信号( $V_{inp}$ ,  $V_{inn}$ )を入力するMOSトランジスタMN1,MN2の利得係数 と、第2のMOS差動回路において2つのゲート電圧( $V_{pc}$ ,  $V_{nc}$ )を入力するMOSトランジスタMN1c,MN2cの利得係数 。との関係が、 。 を満たすものとする。さらに、第1のMOS差動回路に入力される差動電圧信号( $V_{inp}$ ,  $V_{inn}$ )のコモンレベル $V_{com}$ と、第2のMOS差動回路に入力される2つのゲート電圧のコモンレベル $V_{com}$ と、第2のMOS差動回路に入力される2つのゲート電圧のコモンレベル $V_{com}$ と、第2のMOSを満たすものとする。この場合、第2項は0となり、3次歪みをキャンセルすることができる。この場合、時間出力  $V_{com}$ 0 となり、3次歪みをキャンセルすることができる。この場合、時間出力  $V_{com}$ 1 は、以下の式(14)のようになる。

[0056]

【数13】

$$t_{out} \approx GV_{in} - \frac{G}{64(V_{com} - V_{TH})^4} V_{in}^5 \cdots (14)$$

上記式(14)からわかるように、上記実施の形態1よりも、5次歪の大きさを1/4 に低減することができる。

[0057]

また、式(12)からVょを変化させることで、利得Gを変えられることがわかる。したがって、製造ばらつきや温度変動により利得が変化しても、Vょを適切に調整することで、利得を一定に保つことができる。また、上記の解析では、Vpc=Vnc=Vょとして計算を行ったが、Vpc,Vncを独立に調整すれば(すなわちVpc Vncとすれば)、電圧・時間変換器1Bのオフセット成分もキャンセルすることができる。このように、第2のMOS差動回路への差動電圧信号の正側電圧Vpcと負側電圧Vncとの間に、タイミング信号(START信号,STOP信号)に含まれるオフセット成分を打ち消すオフセットを与えるようにしてもよい。

[ 0 0 5 8 ]

実施の形態3.

10

30

20

40

次に、本発明の実施の形態3について説明する。

## [0059]

本実施の形態に係る電圧・時間変換器1Cは、変換回路20及び歪み補正回路30の差動回路の構成が、上記実施の形態1,2に係る電圧・時間変換器1A,1Bと異なる。

#### [0060]

図6に示すように、本実施の形態に係る電圧・時間変換器1Cでは、一対のCMOSとしてのMOSトランジスタMN1,MN2のソース端子が分離されて、各々のソース端子にクロック信号CKにより制御される別のMOSトランジスタ(CMOSスイッチ)MN3A,MN3Bが接続されている。歪み補正回路30においても同様に、MOSトランジスタMN1c,MN2cのソース端子が分離され、各々のソース端子にクロック信号CKにより制御される別のMOSトランジスタ(スイッチ)MN4A,MN4Bが接続されている。このようにすることで、MOSトランジスタMN1,MN2及びMOSトランジスタMN1c,MN2cのソース端子を介した干渉を避けることができ、線形性をさらに改善することができる。

## [0061]

ここでは図示しないが、この実施の形態に係る回路構成は、上記実施の形態2の電圧・時間変換器1Bの構成にも同様に適用することができ、これにより、実施の形態2の電圧・時間変換器1Bの線形性をさらに改善することができる。なお、他の実施の形態においても、ゲート電圧を入力する一対のCMOSのソース端子が分離されて、各々のソース端子にクロック信号CKにより制御される別のCMOSが接続されるようにしてもよい。

### [0062]

実施の形態4.

次に、本発明の実施の形態4について説明する。

#### [ 0 0 6 3 ]

本実施の形態に係る電圧・時間変換器1D(図10参照)の構成及び動作を理解するために、まず、理想的な電圧・時間変換器の特性について説明する。図7に示す電圧・時間変換器1A<sup>1</sup> は、従来の回路構成を有する変換器である。図7に示すように、電圧・時間変換器1A<sup>2</sup> は、容量Cを有するコンデンサ3P,3Nと、コンデンサ3P,3NをプリチャージするMOSトランジスタ(スイッチ)MP1,MP2と、入力信号(Vinp,Vinn)を、クロック信号CKに同期して電流信号(Ip,In)に変換するVI変換器25と、インバータ4P,4Nと、を備える。VI変換器25は、図1に示す、MOSトランジスタMN1,MN2,MN3で構成される回路をまとめたものである。

#### [0064]

## [0065]

【数14】

$$I_{P}(V_{in}) = \frac{1}{a - b(V_{com} + V_{in}/2)}$$

$$I_{N}(V_{in}) = \frac{1}{a - b(V_{com} - V_{in}/2)}$$

...(15)

10

20

30

30

40

ここで、aは任意の定数であり、bは、以下の式(16)を満足する定数である。

[0066]

【数15】

$$b = \frac{2G}{CV_{DD}} \qquad \dots (16)$$

ここで、Gは、電圧・時間変換器1A′の利得である。

#### [0067]

図8に示すように、電圧・時間変換器1A′におけるVI変換器25の伝達関数(実線)と理想的な伝達関数(点線)とを比較する。VI変換器25は、MOSトランジスタMN1,MN2,MN3で構成されるため、VI変換器25における差動電圧Vinと電流(Ip,IN)との間の理想的な伝達関数は、差動電圧Vinの2次関数(上記式(2)参照)となる。電流(Ip,IN)と差動電圧Vinとの間の伝達関数が、点線で示す理想的なものであれば、差動電圧Vinと時間出力t。utとの関係は線形となる。しかしながら、電圧・時間変換器1A′におけるVI変換器25の伝達関数は、直線状となるため、理想的な伝達関数とはほど遠いものとなる。これが、電圧・時間変換器1A′の非線形性の原因となる。

#### [0068]

そこで、本実施の形態に係る電圧・時間変換器1Dは、図9に示すように、2本の直線で理想の伝達関数に折れ線近似された伝達関数に従って動作する。これにより、図7に示す電圧・時間変換器1A′よりも線形性を改善することができる。

# [0069]

図10に示すように、電圧・時間変換器1Dは、変換回路21と、補正回路31と、を備える。

## [0070]

# [0071]

# [0072]

補正回路 3 1 は、第 1 の電流組(I <sub>P 1</sub> , I <sub>N 1</sub> ) に、補正電流としての第 2 の電流組 (I <sub>P 2</sub> , I <sub>N 2</sub> ) 及び第 3 の電流組(I <sub>P 3</sub> , I <sub>N 3</sub> ) を加える。

#### [0073]

50

10

20

30

図10に示すように、補正回路31は、第3のMOS差動回路としてのMOS差動回路 31Aと、第4のMOS差動回路としてのMOS差動回路31Bと、を備える。

## [0074]

MOS差動回路31Aは、MOSトランジスタMNI4,MNI5,MNI6及び抵抗RI3、RI4を備える。MOSトランジスタMNI4とMOSトランジスタMNI6との間に抵抗RI3が挿入され、MOSトランジスタMNI5とMOSトランジスタMNI6との間に抵抗RI4が挿入されている。MOSトランジスタMNI4は、ノードDPとMOSトランジスタMNI6との間に挿入され、差分電圧信号(Vinp,Vinn)の正側電圧信号Vinpをゲート電圧として入力する。また、MOSトランジスタMNI5は、ノードDNとMOSトランジスタMNI6との間に挿入され、差分電圧信号(Vinp,Vinn)の負側電圧信号Vinnをゲート電圧として入力する。MOSトランジスタMNI6は、クロック信号CKを入力し、MOSトランジスタMNI4,MNI5と電圧Vs1が印加される端子との間に挿入される。

# [0075]

MOS差動回路31Aは、第2の電流組( $I_{P2}$ ,  $I_{N2}$ )を出力する。差動電圧 $V_{i}_{n}$ に対する第2の電流  $I_{P2}$ の伝達関数は、図11に示すように、差動電圧 $V_{in}_{n}$ に比例して増加する直線となる。この増加直線の傾きは抵抗 R I 3 , R I 4 の値で調整することができる。第2の電流  $I_{P2}$  は、 $V_{in}_{n}$  <  $V_{s1}$  +  $V_{TH}$  の範囲では流れない。 $V_{s1}$  は、MOSトランジスタMNI6のオフセット電圧であり、電圧  $V_{TH}$  は、MOSトランジスタMNI6のオフセット電圧であり、電圧  $V_{TH}$  は、MOSトランジスタMNI6のオフセット電圧であり、電圧  $V_{TH}$  は、MOSトランジスタMNI6のよりに電圧である。第2の電流  $I_{P2}$  が流れ出す差動電圧  $V_{in}_{n}$  は、電圧  $V_{s1}_{n}$  の値により調整できる。このことは、第2の電流  $I_{N2}$  も同様である。このように、MOS差動回路31Aは、差動電圧信号( $V_{in}_{p}$ ,  $V_{in}_{n}$ )をゲート電圧として入力し、一対の抵抗  $V_{in}_{n}$  の電流組( $V_{in}_{n}$  を補正電流として出力する。

# [0076]

また、図10に示すように、MOS差動回路31Bは、MOSトランジスタMNI7,MNI8,MNI9を備える。MOSトランジスタMNI7は、ノードDPとMOSトランジスタMNI9との間に挿入され、MOSトランジスタMNI8は、ノードDNとMOSトランジスタMNI9との間に挿入される。MOSトランジスタMNI9は、クロック信号CKを入力し、MOSトランジスタMNI7,MNI8とグラウンドとの間に挿入される。MOSトランジスタMNI7,MNI8に入力されるゲート電圧は、一定の電圧(Vpc,Vnc)である。

# [0077]

MOS差動回路 3 1 B は、第 3 の電流組( $I_{P3}$ ,  $I_{N3}$ )を出力する。 MOSトランジスタMNI7,MNI8のゲート電圧として一定の電圧( $V_{pc}$ ,  $V_{nc}$ )が印加されるため、差動電圧  $V_{in}$ に対する第 3 の電流  $I_{P3}$ の伝達関数は、図 1 1 に示すように、差動電圧  $V_{in}$ によらず一定となる。第 3 の電流  $I_{P3}$ の大きさは、ゲート電圧( $V_{pc}$ ,  $V_{nc}$ )の値で調整することができる。このことは、第 3 の電流  $I_{N3}$ も同様である。 MOS 差動回路 3 1 B は、一定の電圧( $V_{pc}$ ,  $V_{nc}$ )をゲート電圧として入力し、一定の電組組( $I_{P3}$ ,  $I_{N3}$ )を補正電流として出力する。

# [0078]

これら第1の電流  $I_{P_1}$ 、第2の電流  $I_{P_2}$ 、第3の電流  $I_{P_3}$  はノード D P で加算されて、電流  $I_{P_3}$  となる。また、第1の電流  $I_{N_1}$ 、第2の電流  $I_{N_2}$ 、第3の電流  $I_{N_3}$  は、加算されて電流  $I_{N_3}$  となる。したがって、インバータ4 P ,4 N に入力される一対の電流( $I_{P_1}$  , $I_{N_1}$  )の伝達関数 は、図11に示すようになり、理想的な伝達関数に折れ線近似されたものとなる。この結果、差動電圧  $V_{i_n}$  に対する時間出力  $t_{out}$  の線形性が向上する。

## [0079]

## 実施の形態5.

次に、本発明の実施の形態5について説明する。

10

20

30

10

20

30

40

50

[0800]

図12に示すように、本実施の形態に係る電圧・時間変換器1Eは、変換回路21と、補正回路32と、を備える。すなわち、電圧・時間変換器1Eは、補正回路31の代わりに補正回路32を備える点が、電圧・時間変換器1Dと異なる。

[0081]

変換回路 2 1 は、差動電圧信号 ( $V_{inp}$ ,  $V_{inn}$ ) を一対の電流 ( $I_{P1}$ ,  $I_{N1}$ ) に変換する。この ( $I_{P1}$ ,  $I_{N1}$ ) を、第 1 の電流組とする。

[0082]

図12に示すように、補正回路32は、第3のMOS差動回路としてのMOS差動回路31Aと、第4のMOS差動回路としてのMOS差動回路31Bと、を備える点は補正回路31と同じである。補正回路32は、第3のMOS差動回路としてのMOS差動回路31Cをさらに備える。

[0083]

MOS差動回路31Cは、MOSトランジスタMNI10,MNI11,MNI12及び抵抗RI5、RI6を備える。MOSトランジスタMNI10とMOSトランジスタMNI11とMOSトランジスタMNI11とMOSトランジスタMNI110とMOSトランジスタMNI110とMOSトランジスタMNI110とMOSトランジスタMNI110に抵抗RI6が挿入されている。MOSトランジスタMNI10には、ノードDPとMOSトランジスタMNI12との間に挿入され、差分電圧信号(Vinpをゲート電圧として入力する。また、MOSトランジスタMNI11は、ノードDNとMOSトランジスタMNI112との間に挿入され、差分電圧信号(Vinpをゲート電圧として入力する。MOSトランジスタMNI12は、クロック信号CKを入力し、MOSトランジスタMNI11と電圧Vs2が印加される端子との間に挿入される。

[0084]

[0085]

これら第1の電流  $I_{P_1}$ 、第2の電流  $I_{P_2}$ ,第3の電流  $I_{P_3}$ 、第4の電流  $I_{P_4}$ は ノード D P で加算されて、電流  $I_p$  となる。また、第1の電流  $I_{N_1}$ 、第2の電流  $I_{N_2}$ ,第3の電流  $I_{N_3}$ 、第4の電流  $I_{N_4}$ は ノード D N で加算されて電流  $I_N$  となる。 したがって、インバータ4 P ,4 N に入力される、差動電  $I_N$  に対する一対の電流( $I_P$  ,  $I_N$ )の伝達 関数 は、図13に示すようになり、理想的な伝達 関数に折れ線近似される。この結果、差動電  $I_N$  に対する時間 出力  $I_N$  。  $I_N$  の線 形性 が向上する。

[0086]

このように、本実施の形態では、図13に示すように、3本の直線で理想的な伝達関数に折れ線近似した。補正回路32の第3のMOS差動回路の数をさらに増やして、4本以上の直線で理想的な伝達関数に折れ線近似することも可能である。

[0087]

実施の形態 6.

次に、本発明の実施の形態6について説明する。

[0088]

上記実施の形態1、2、3、4、5では、差動電圧信号から時間出力に線形変換する電

圧・時間変換器 1 A , 1 B , 1 C , 1 D , 1 E について説明した。これらの電圧・時間変換器 1 A , 1 B , 1 C , 1 D , 1 E によれば、差動電圧信号( $V_{inp}$ ,  $V_{inn}$ ) から時間出力  $t_{out}$  への線形性が向上し、変換精度を向上することができる。

[0089]

電圧・時間変換器1A,1B,1C,1D,1Eを用いてアナログ・デジタル変換器を構成するためには、電圧・時間変換器1A,1B,1C,1D,1Eの後段に、時間出力をデジタルデータ信号に変換する並列型の時間・デジタル変換器を取り付ける必要がある。しかし、並列型の時間・デジタル変換器を使用すると、変換精度を上げると回路規模と変換時間が指数関数的に増加してしまい、消費電力が増加し、動作速度が低下するおそれがある。

[0090]

そこで、本実施の形態では、変換精度を上げても消費電力の増加、動作速度の低下が起こらない時間領域のアナログ・デジタル変換器について説明する。本実施の形態に係るアナログ・デジタル変換器では、サブレンジング方式が用いられる。サブレンジング方式は、アナログ・デジタル変換を、粗い変換と細かい変換の2回に分けて、必要な回路規模を縮小する。

[0091]

図14に示すように、本実施の形態に係るアナログ・デジタル変換器100では、電圧・時間変換器1Bと時間・デジタル変換器10とを組み合わせて上位AD変換器としてのアナログ・デジタル変換器CADC、下位AD変換器としてのアナログ・デジタル変換器FADCとを構成する。アナログ・デジタル変換器100は、このアナログ・デジタル変換器CADC、FADCの他、残差発生回路50と、合成器としてのエンコーダ60と、を備える。

[0092]

アナログ・デジタル変換器 CADC は、入力した差動電圧信号( $V_{inp}$ ,  $V_{inn}$ ) を、 n ( n は自然数 ) ビットのデジタル信号のうちの上位 m ( m は n より少ない自然数 ) ビットの上位デジタルデータ信号 DOUT < m - 1 : 0 > に変換する。

[0093]

残差発生回路 5 0 は、差動電圧信号( $V_{inp}$ ,  $V_{inn}$ ) と、アナログ・デジタル変換器 C A D C から出力された上位デジタルデータ信号 D O U T < m - 1 : 0 > とに基づいて、差動電圧信号( $V_{inp}$ ,  $V_{inn}$ ) の残差信号を発生させる。

[0094]

アナログ・デジタル変換器 FADCは、残差信号を入力し、残差信号を n ビットのデジタル信号のうちの下位 n - m ビットの下位デジタルデータ信号 DOUT < (n - m) - 1:0 > に変換する。

[0095]

エンコーダ 6 0 は、上位デジタルデータ信号 D O U T < m - 1 : 0 > と、下位デジタルデータ信号 D O U T < (n - m) - 1 : 0 > とを合成して、 n ビットのデジタル信号 D O U T < n - 1 : 0 > として出力する。

[0096]

アナログ・デジタル変換器CADC,FADCでは、電圧・時間変換器1Bを用いているので、差動電圧信号(V<sub>inp</sub>,V<sub>inn</sub>)から時間出力 t<sub>out</sub>への線形変換の線形性が改善されている。なお、本実施の形態では、電圧・時間変換器1Bの代わりに、同じく線形性が改善された電圧・時間変換器1A,1C,1D,1Eを用いるようにしてもよい

[0097]

図 1 5 には、時間・デジタル変換器 1 0 の回路構成の一例が示されている。時間・デジタル変換器 1 0 は、 S T A R T 信号と S T O P 信号の立ち上がリエッジの時間差(時間出力 t  $_{out}$ )を k ( k はmまたは  $_{nut}$ ) を k ( k はmまたは  $_{nut}$ ) を k ( k はmまたは  $_{nut}$ ) を k ( k はmまたは  $_{nut}$ ) と k ( k はmまたは  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m または  $_{nut}$ ) と k ( k は m またな  $_{nut}$ ) と k ( k は m またな  $_{nut}$ ) と k ( k は m またな  $_{nut}$ ) と k ( k は m またな  $_{nut}$ ) と k ( k は m またな  $_{nut}$ ) と k ( k は m またな  $_{nut}$ ) と k ( k は m またな  $_{nut}$ ) と k ( k は m またな  $_{nut}$ ) と k ( k は m またな  $_{nut}$ ) と k ( k は m またな  $_{nut}$ ) と k ( k は m またな  $_{nut}$ ) と k ( k は m またな  $_{nut}$ ) と k ( k は m またな  $_{nut}$ ) と k ( k は m またな

10

20

30

40

ンコーダ11とを備える。

## [0098]

START信号が立ち上がると、その立ち上がり信号が、遅延回路D1~D2<sup>k</sup>で遅延しながら伝搬されていく。その後、STOP信号が立ち上がると、遅延回路D1~D2<sup>k</sup>の出力はそれぞれフリップフロップFF1~FF2<sup>k</sup>によりラッチされる。フリップフロップFF1~FF2<sup>k</sup>の出力を見ることで、STOP信号が立ち上がった時刻にSTART信号の立ち上がりが何段目の遅延回路まで伝搬したかをエンコーダ11が検出する。エンコーダ11は、入力したタイミング信号(START信号、STOP信号)を、デジタル信号DOUT<k-1:0>に変換して出力する。この際の1LSB(時間分解能)は、1つの遅延回路の遅延時間tヵdに等しくなる。

[0099]

図16には、時間・デジタル変換器10の回路構成の他の例が示されている。この時間・デジタル変換器10では、遅延回路D1~D $2^k$ 間に補間回路IP1~IP $2^{k-1}$ が設けられている。補間回路IP1~IP $2^{k-1}$ には  $t_{p-d}$ だけ時間がずれた2つの立ち上がり信号が入力される。補間回路IP1~IP $2^{k-1}$ は、2つの信号の中間の時刻で立ち上がるパルス信号を出力する。これにより、  $t_{p-d}$  / 2間隔で立ち上がるパルス列が得られる。このパルス列をSTOP信号の立ち上がりエッジでラッチすることにより、  $t_{p-d}$  / 2の時間分解能で時間・デジタル変換を行うことができる。

[0100]

時間・デジタル変換器10では、時間分解能が高いほど、変換時間を短縮することできる。この図16に示す構成を採用することで、アナログ・デジタル変換器100の変換速度を向上することができる。また、図16では、補間を1度行う構成を示しているが、複数回補間を行うことで、さらに時間分解能を上げるようにしてもよい。

[0101]

差動電圧信号( $V_{inp}$ 、 $V_{inn}$ )は、上位 A D 変換を行うアナログ・デジタル変換器 C A D C の電圧・時間変換器 1 B により時間出力  $t_{out}$  に変換され、その時間出力  $t_{out}$  を時間・デジタル変換器 1 0 によりデジタル変換し、上位 m ビットの変換結果が得られる。

[0102]

図17には、アナログ・デジタル変換器CADCの出力が2ビット(m = 2)の場合に対応する残差発生回路50の回路構成が示されている。図17に示すように、残差発生回路50は、コンデンサC0~C2と、スイッチS0~S3とを備える。コンデンサC0~C2の容量値はC0=C1=C,C2=2Cに設定されている。VTは入力される電圧信号の上限電圧であり、VBは入力される電圧信号の下限電圧であり、アナログ信号である電圧信号の入力範囲を規定する。

[0103]

V<sub>com</sub>は、出力端子OUTP、OUTNのコモンレベルを規定する電圧である。正側電圧信号V<sub>inp</sub>を取り込むトラック期間では、スイッチS0~S2は、正側電圧信号V<sub>inp</sub>が入力される入力端子INPに接続され、スイッチS3は、V<sub>com</sub>が入力される端子に接続している。

[0104]

トラック期間が終了すると、スイッチS0~S4はオフとなり、トラック期間終了時の 正側電圧信号V<sub>i n p</sub>がコンデンサC0~C2にサンプリングされる。

[0105]

その後、残差発生回路50は、アナログ・デジタル変換器CADCの変換結果DOUT [1:0]に応じてスイッチS0~S2を切り替える。すなわち、残差発生回路50は、 DOUT[0]が1ならば、スイッチS1をVTへ接続し、0ならばVBへ接続する。残 差発生回路50は、スイッチS2も同様に、DOUT[1]が1ならばVTへ接続し、0 ならばVBへ接続する。このようにすると、コンデンサC0~C2に蓄えられていた電荷 が再配分され、出力端子OUTPには、残差電圧信号(Vinp,Vinn)から並列型の 10

20

30

40

アナログ・デジタル変換器 C A D C の変換結果を差し引いた残差信号が出力端子 O U T P から出力される。なお、残差発生回路 5 0 は、入力端子 I N N、出力端子 O U T N が接続されるブロックの回路構成も、上述した回路構成と同じである。

### [0106]

この容量型の残差発生回路50は、コンデンサC0~C2とスイッチS0~S4のみで構成できるため、面積、消費電力が小さいという利点がある。

#### [0107]

図14に戻り、アナログ・デジタル変換器100の全体の動作について説明する。アナログ・デジタル変換器100は、残差発生回路50により、アナログ・デジタル変換器CADCで得られる粗い変換結果(上位デジタル信号)を差動電圧信号(V<sub>inp</sub>,V<sub>inn</sub>)から差し引き、残差信号を発生する。この残差信号は、細かい変換を行うアナログ・デジタル変換器FADCは、残差信号を入力して、電圧・時間変換器1A,1Bにより時間出力 toutに変換し、その時間出力 toutを時間・デジタル変換器10によりデジタル変換し、下位ビットの変換結果(下位デジタル信号)を得る。粗い変換結果と、細かい変換結果は、合成器としてのエンコーダ60で合成され、nビットのデジタルデータ信号DOUT<n-1:0>として出力される。

## [0108]

また、仮に8ビットのアナログ・デジタル変換を、サブレンジング方式を使用しないで構成した場合には、8ビットの並列型の時間・デジタル変換器が必要となる。この場合には、2<sup>8</sup>(256)個の遅延回路と時間比較器が必要となる。一方で、本実施の形態のように、粗い変換4ビット、細かい変換4ビットのサブレンジング構成とすると、4ビットの時間・デジタル変換器10が2組必要となり、遅延回路と時間比較器は32個で済む。このため、大幅な電力削減が可能となる。また、時間・デジタル変換器10の変換時間は、この遅延回路の数に比例するため、変換時間も大幅に短縮することができる。

#### [0109]

入力される差動電圧信号( $V_{inp}$ ,  $V_{inn}$ ) が大きい場合には、高線形な電圧・時間変換器 1 A , 1 B は、高精度なデジタル信号 D < n - 1 : 0 > を得るために特に有用である。

# [0110]

以上詳細に説明したように、本実施の形態によれば、差動電圧信号( $V_{inp}$ ,  $V_{inn}$ )を入力し、該差動電圧信号( $V_{inp}$ ,  $V_{inn}$ )を時間出力  $t_{out}$ に に は 形変換する場合に、 時間出力  $t_{out}$ に 含まれる 差動電圧信号( $V_{inp}$ ,  $V_{inn}$ )の 3 次成分を除去することができるので、 良好な 線形性を 得ることができる。

## [0111]

また、本実施の形態によれば、差動電圧信号(V<sub>inp</sub>, V<sub>inn</sub>)を入力し、該差動電圧信号(V<sub>inp</sub>, V<sub>inn</sub>)を時間出力 t<sub>out</sub>に線形変換する場合に、電圧と電流との間の伝達関数を理想の伝達関数に近づけることができるので、良好な線形性を得ることができる。すなわち、本実施の形態によれば、差動電圧信号を時間出力に変換する場合に、その線形性を保つために一対のパルス電圧信号に対応する一対の電流を補正するので、良好な線形性を得ることができる。

# [0112]

なお、電圧・時間変換器1A~1Cの構成と、電圧・時間変換器1D~1Eの構成とを 組み合わせて電圧・時間変換器を構成するようにしてもよい。

# [0113]

このように、上記各実施の形態によれば、高線形な電圧・時間変換器1A,1B,1C,1D,1Eを提供することができる。また、この電圧・時間変換器1A,1B,1C,1D,1Eを用いてサブレンジング構成の時間領域のアナログ・デジタル変換器CADC,FADCを構成することで、変換精度を上げても消費電力増加、動作速度低下が起こらないアナログ・デジタル変換器100を提供することができる。

# [0114]

40

30

10

20

この発明は、この発明の広義の精神と範囲を逸脱することなく、様々な実施の形態及び変形が可能とされるものである。また、上述した実施の形態は、この発明を説明するためのものであり、この発明の範囲を限定するものではない。すなわち、この発明の範囲は、実施の形態ではなく、特許請求の範囲によって示される。そして、特許請求の範囲内及びそれと同等の発明の意義の範囲内で施される様々な変形が、この発明の範囲内とみなされる。

#### 【産業上の利用可能性】

## [ 0 1 1 5 ]

この発明は、アナログ・デジタル変換器等に適用することができる。

## 【符号の説明】

## [0116]

1 A , 1 B , 1 C , 1 D , 1 E , 1 A ' 電圧・時間変換器、 2 P , 2 N 電源電圧端子、 3 P , 3 N コンデンサ、 4 P , 4 N インバータ、 1 0 時間・デジタル変換器、 1 1 エンコーダ、 2 0 , 2 1 変換回路、 2 5 V I 変換器、 3 0 歪み補正回路、 3 1 , 3 2 補正回路、 3 1 A , 3 1 B , 3 1 C M O S 差動回路、 5 0 残差発生回路、 6 0 エンコーダ、 1 0 0 アナログ・デジタル変換器、 D P , D N ノード、 D 1 ~ D 2 <sup>k</sup> 遅延回路、 F F 1 ~ F F 2 <sup>k</sup> フリップフロップ、 M P 1 , M P 2 , M N 1 , M N 2 , M N 3 , M N 1 c , M N 2 c , M N 4 , M N 3 A , M N 3 B , M N 4 A , M N 4 B , M N I 4 , M N I 5 , M N I 6 , M N I 7 , M N I 8 , M N I 9 , M N I 1 0 , M N I 1 1 1 , M N I 1 2 M O S トランジスタ、 R I 1 , R I 2 , R I 3 , R I 4 , R I 5 , R I 6 抵抗、 I P 1 ~ I P 2 <sup>k - 1</sup> 補間回路

# 【図1】

# 【図2】

10

# 【図3】

# 【図4】

# 【図5】

# 【図6】

# 【図7】

# 【図8】

# 【図9】

【図16】

【図17】